Тестването на интегрални схеми се отнася до процеса на тестване на производителността, функционалността и надеждността на интегрирани схеми .Целта на тестването на интегрални схеми е да се увери, че интегралните схеми могат да отговорят на изискванията за проектиране и целите за производителност в практическите приложения, и да се подобри надеждността и стабилността на интегралните схеми.

Тестването на ИС включва число аспекти, като функционално тестване, тестване на производителност, тестване на надеждност, параметрично тестване и други. Функционалното тестване главно проверява дали логическата функция на ИС е правилна; тестът за производителност главно проверява времевата производителност на ИС, производителността по отношение на разхода на енергия и т.н.; тестът за надеждност главно проверява устойчивостта на ИС срещу помешения, продължителността на живот и т.н.; параметричното тестване главно проверява параметричната производителност на ИС, като например напрежение, ток, честота и т.н.

Основният принцип на тестването на ИС

1. Генериране и предаване на тестови сигнали

Основният принцип на теста на ИС е да се генерират и предават тестови сигнали за тестване на производителността, функционалността и надеждността на интегрираните кръгове. Тестовите сигнали могат да бъдат аналогови, цифрови или смесени сигнали, които се избират според тестовите изисквания и цели.

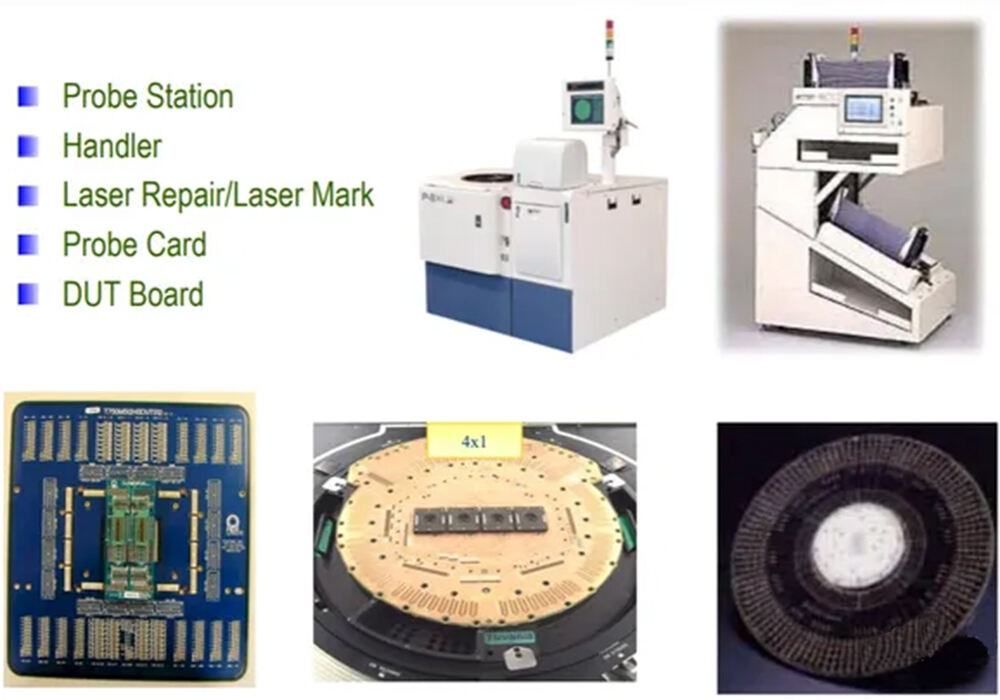

Генерирането на тестови сигнали може да се постигне чрез тестови инструменти, тестово оборудване или тестов софтуер. Предаването на тестови сигнали може да се реализира чрез тестови зонди, тестови фиксации или тестови интерfeйси. Генерирането и предаването на тестови сигнали трябва да отговарят на определени изисквания за точност, стабилност и надеждност, за да се гарантира точността на резултатите от тестовете.

2. Придобиване и анализ на тестов отговор

Друг основен принцип за тестването на ИС е оценката на производителността, функционалността и надеждността на ИС чрез придобиване и анализ на тестови отговори. Тестовият отговор може да бъде параметри като напрежение, ток, честота и т.н., или показатели за производителност като логически състояния и времеви характеристики.

Придобиването на тестов отговор може да се осъществи чрез тестови инструменти, тестово обзавеждане или тестов софтуер. Анализът на тестовия отговор може да се постигне чрез анализ на данни, оценка на производителността или диагностика на повреди. Събирането и анализът на тестовия отговор трябва да отговарят на определени изисквания за точност, стабилност и надеждност, за да се гарантира точността на резултатите от теста.

3. Оценка и обратна връзка на резултатите от теста

Основното principio на тестването на ИС включва също така оценката и обратната връзка на резултатите от теста. Оценката на резултатите от теста е да се провери дали производителността, функционалността и надеждността на ИС отговарят на проектните изисквания и целите за производителност чрез сравнение на разликата между тестовия отговор и очаквания отговор.

Обратната връзка за резултатите от тестовете се използва, за да оптимизира и подобри дизайна, производството или процеса на тестване на ИЧ чрез комуникиране на резултатите от тестовете до проектиращите, производителите или тестващите. Съдъжението и обратната връзка по резултатите от тестовете трябва да отговарят на определени изисквания за реално време, точност и надеждност, за да се гарантира ефективността на процеса на тестване.

Функционалният тест е основен метод за тестване на ИЧ и се използва предимно за проверка дали логическата функция на ИЧ е правилна. Функционалното тестване обикновено използва Векторно тестване, за да се наблюдава дали изходната реакция на ИЧ отговаря на очакванията при въвеждане на специфични тестови вектори.

Преимуществото на функционалното тестване е, че осигурява висока покритост на тестовете и може да открива повечето логически грешки в ИЧ. Недостатъкът на функционалното тестване обаче е, че отнема много време и изисква голямо количество тестови вектори и данни за тестове.

Тестът на производителността е важен метод за тестиране на ИС, използван главно за разпознаване на времевите характеристики и показателите за разход на енергия на ИС. Тестът на производителността обикновено използва Тест на Време и Тест на Мощност, за да оценя параметрите на производителността на ИС чрез измерването на техните времеви параметри и параметри на разход на енергия.

Преимуществото на теста на производителността е, че може да открива проблеми с бутилското грдие на производителността и разхода на енергия на ИС. Недостатъкът на теста на производителността обаче е, че изисква тестови устройства с висока точност и сложни процедури за тест.

Тестът на надеждността е ключов метод за тестиране на ИС, използван основно за разпознаване на нивото им на устойчивост към помешения и техния ресурс на живот. Тестът на надеждността обикновено използва Стресов тест, Тест на стареене и Околков тест, за да оцени надеждността на ИС чрез симулиране на различни стресови условия и работни режими.

Преимуществото на тестовете за надеждност е, че те могат да откриват потенциални проблеми и въпроси свързани с продължителността на ИК. Всичко пак, недостатъкът на тестовете за надеждност е, че това изисква много време и много тестово оборудване и условия.

Параметрическият тест е допълнителен метод за тест на ИК, който се използва предимно за проверка на напрежението, тока и честотата на ИК, както и другите параметри на производството. Параметрическият тест обикновено използва специални инструменти за параметричен тест, като измерва стойностите на параметрите на ИК, за да оценят нейните производителни показатели.

Преимуществата на параметрическото тестирование са бърза скорост на теста и простота в операцията. Всичко пак, недостатъкът на параметрическото тестирание е, че покритието е ниско и не може да открива логически грешки и ограничения в производителността на ИК.